Содержание команды

Модульный принцип построения. Этот принцип предполагает разделение электрической схемы МПУ на функционально завершенные модули. Исходя из классической схемы вычислительногоустройства, любое МПУ должно включать как минимум микропроцессор, ЗУ и УВВ. Конструкция модуля представляет собой либо функциональную ячейку (ФЯ) (см. § 2.3), либо микросборку (МСБ), либо СБИС. Современные модули МПУ чаще всего выполняются в виде ФЯ. Приведенный выше состав модулей позволяет построить универсальное МПУ. При решении вопроса о функциональном составе модулей МПУ необходимо учитывать многофункциональность (универсальность) и специализацию модулей. Повышение универсальности модулей обеспечивает сокращение их. номенклатуры, снижение затрат на проектирование. Специализация модулей является средством достижения соответствия структуры МПУ выполняемым алгоритмам и тем самым повышения быстродействия, а следовательно, и эффективности применений1 МПУ в РЭА.

Модульный принцип конструирования МПС дает возможность, разработчику выбирать только необходимые ему модули и постепенно наращивать функциональные возможности МПУ. Иногда при проектировании МПУ, реализующих конкретные алгоритмы, для обеспечения требуемых характеристик достаточно небольшой фрагмент алгоритма реализовать аппаратно. Конструирование специального модуля или БИС для реализации такого фрагмента может оказаться неоправданно дорогим. Целесообразно на модуле МП установить специальный соединитель для подключения малых модулей, реализующих конкретные функции. Такой подход был реализован в микромодульных платах iSBX [3].

Для расширения функциональных возможностей одноплатной микро-ЭВМ разработаны три модуля: последовательного вводавывода iSBXx25i, параллельного ввода-вывода iSВХх350 и арифметического процессора с плавающей точкой iSВX332.

При менение таких модулей увеличивает гибкость одноплатной микро-ЭВМ. Для обеспечения аппаратной специализации системы разработана переходная плата iSBXyx960=5, содержащая пять гнезд шины iSBX, к которым разработчик может подключать специальные аппаратные модули.

Модульный принцип построения позволяет повысить эффективность применения МПС для конкретных задач. Это достигается выбором типа и числа модулей, учитывающих особенности решаемого алгоритма. Например, микро-ЭВМ «Электроника С5-12» в минимальной конфигурации представляет собой микропроцессор, содержащий ПЗУ емкостью 1КХ32 и ОЗУ емкостью 128X16. Микро-ЭВМ может использоваться совместно с модулями «Электроника С5-121» — АЦП (число каналов 115, время преобразования 10 мс, погрешность 0,4%), «Электроника С5-125» — модуль внешнего ОЗУ емкостью 8К байт, «Электроника C5-I123» — модуль сопряжения с устройством ввода-вывода и некоторыми другими.

Комбинируя модули, можно получать вычислительные средства различного назначения. Приведем некоторые из них: микро-ЭВМ+ +ОЗУ — минимальная конфигурация одноплатной микро-ЭВМ с относительно большим объемом памяти, микро-ЭВМ + АЦП — применяется в измерительных приборах, цифровых следящих системах.

Магистральный принцип обмена информацией. Некоторые выводы МПС должны соединяться с различными внешними устройствами. Это обеспечивается объединением выводов МПС в магистрали (шины) и мультиплексированием во времени обмена информацией между модулями. Весь информационный поток, циркулирующий в МПС, обычно разбивается на три группы: адреса, дан-яые и управление. В соответствии с этим выделяют шину данных, шину адресов и управляющую шину. Применяя последовательно временное мультиплексирование, можно построить МПС с трех-, двух- и однотипной структурой.

При выборе структуры МПУ необходимо учитывать следующее: при уменьшении числа шин увеличивается площадь кристалла или модуля, отводимая под функциональные элементы, и тем самым повышаются функциональные возможности МПС.

Вместе с тем применение временного мультиплексирования обмена информацией приводит к снижению быстродействия и необходимости использования дополнительных буферных регистров.

В некоторый период времени только два устройства могут быть одновременно подключены к шине. Одно из них — ведущее, другое — ведомое. Ведущим устройством обычно является МП. При обмене информацией между МП и ведомым остальные устройства, подключенные к шине, не должны им мешать. Такое раздельное использование шины достигается различными способами подключения к ней выводов устройств. Известны три способа подключения: логическое объединение, объединение с помощью схем с открытым коллектором и объединение с использованием схем с тремя состояниями [4].

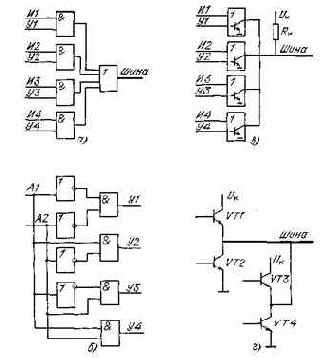

Логическое объединение выполняется с помощью логических схем ИЛИ, И (рис. 1.2,а). На входы логических вентилей поступают информационные сигналы И1 — И4. Подключением этих сигналов к шине управляют сигналы У1 — У4, схема формирования которых приведена на рис. 1.2,6. На вход схемы поступают два адресных сигнала: Al и А2. Схема формирует четыре взаимоисключающих управляющих сигнала У1

— У4. (Вместо этой схемы может быть использован любой дешифратор типа 1 из и на два входа и более. Максимальное число подключаемых устройств определяется числом входов логического элемента ИЛИ.

Объединение с помощью схем с открытым коллектором предполагает электрическое соединение выходов нескольких логических элементов, как это показано на рис. 1.2,в. В схемах с открытым коллектором отсутствует .нагрузочный резистор. Выходы схем с открытым коллектором объединены с использованием общего нагрузочного резистора RK. Выходной сигнал равен 0, если сигнал на любом из объединенных выходов равен 0, и 1, если сигналы на всех объединенных выходах равны 1. По аналогии с реализуемой логической функцией такой способ подключения называют «монтажным ИЛИ», или «монтажным И». При поступлении на вход управляющего сигнала 1, на выходе схемы ИЛИ появляется 1 (независимо от значения информационного сигнала И); в результате общий выходной сигнал не меняется.

При ( низком уровне управляющего сигнала сигнал на выходе схемы ИЛИ равен информационному. Итак, если один управляющий сигнал равен 0, а остальные II, то общий выходной сигнал повторяет значение информационного входа схемы ИЛИ, имеющей низкое значение сигнала управления.

Для подключения устройств к шине с использованием схем с открытым коллектором требуется меньшее число логических элементов, чем при логическом объединении. Однако шины на схемах с открытым коллектором (как и шины с логическим объединением) имеют ограниченное применение. В основном, это обусловлено следующими причинами:

1. Значение выходного тока стандартной управляющей схемы, выполненной по ТТЛ-технологии, около 20 мА. Поэтому с помощью «монтажного ИЛИ» можно объединить сравнительно немного (не более 20) схем с открытым коллектором.

Рис. 1.2. Структурные схемы подключения выходов нескольких микросхем к общей шине:

а — логическое объединение сигналов; б — схема формирования управляющих сигналов; в — подключение с помощью схем с открытым коллектором; г — подключение с помощью схем с тремя состояниями

2. Нагрузочный резистор занимает место на плате и потребляет около 1 мА, когда шина находится в рабочем состоянии. Наличие этого тока еще больше снижает уровень сигнала в шине.

Объединение с использованием схем с тремя состояниями свободно от недостатков, присущих рассмотренным выше способам. На рис. 1.2,г нагрузочными являются транзисторы VT1 и VT3. На входы транзисторов подаются управляющие и информационные сигналы. Каждая пара транзисторов управляет подключением одного устройства. При подключении устройства к шине транзисторной парой управляет информационный сигнал. Например, при подаче лог. 1 на VT1 и лог. 0 на VT2 транзистор VT1 открыт, VT2 закрыт; на шине — лог. 1. Если на VT1 подается 0, а на VT2 1, то на шине — лог. 0. Одновременно значение управляющего сигнала на входах транзисторов VT3, VT4 равно 0.

Оба транзистора закрыты, и схема находится в третьем устойчивом состояния: «цепь разомкнута». В этом состоянии через схему протекает очень маленький ток. Шины с тремя состояними имеют следующие преимущества:

схема в состоянии «цепь разомкнута» потребляет ток не более 0,4 мА (схема с открытым коллектором около 2 мА), поэтому в схемах с тремя состояниями можно объединить гораздо больше выходов (до 50);

не требуется дополнительных логических схем. Микропроцессорные БИС имеют буферные схемы с тремя состояниями внутри кристалла, для этого предусматривается дополнительный вывод;

нет необходимости использовать нагрузочный резистор.

При разработке МПУ логическое объединение и объединение с помощью схем с открытым коллектором используются обычно при организации внутренних шин МП, модулей ОЗУ, ПЗУ и др. При организации внешних по отношению к МП шин обычно используются схемы с тремя состояниями.

Наращиваемость вычислительной мощности МП С. Основным отличием МПС от других изделий вычислительной техники является реализация их в виде одной или нескольких БИС. Современные уровни развития полупроводниковой технологии и материаловедения позволяют производить БИС на кристаллах площадью» до 50 мм2. Небольшая площадь кристалла приводит к необходимости расчленения МПУ на отдельные БИС. Факторами, ограничивающими функциональную сложность этих БИС, являются число выводов и потребляемая мощность. Последний фактор особенно важен для .быстродействующих МП БИС, выполненных по биполярной технологии.

Современные МПК БИС включают несколько десятков БИС различного назначения. Разрядность МП БИС обычно составляет 4, 8, реже 16 бит. Микропроцессорные БИС с ограниченной разрядностью называются секционированными. Обеспечение требуемой разрядности проектируемых МПУ достигается путем объединения необходимого числа БИС. При этом обычно не требуется дополнительных аппаратных затрат, достаточно только объединить соответствующие выводы и цепи сигналов переноса.

Более подробно этот вопрос будет рассмотрен в § 1.2. Детальный анализ проблем построения различных МПС на секционированном МПК БИС Ат2900 рассмотрен в [5].

Таким образом, основные принципы построения МПС: микропрограммное управление, модульность построения, магистралыклй обмен информацией и наращиваемость вычислительной мощности позволяют разрабатывать МПУ, структура, система команд, быстродействие и разрядность которых учитывают особенности реализуемых алгоритмов.

1.2. МИКРОПРОЦЕССОРНЫЕ КОМПЛЕКТЫ БИС

Микропроцессорные средства включают: МПК БИС, однокристальные и одноплатные микропроцессоры, микро-ЭВМ, микроконтроллеры, устройства ввода-вывода, хранения, отображения, коммутации информации и т. п. Основой построения МПС являются: МПК БИС, микросхемы запоминающих устройств и преобразования вида информации (АЦП, ЦАП).

Микропроцессорный комплект БИС представляет собой набор электрически совместимых цифровых БИС, достаточный для построения различных МПУ. Существующие МПК БИС можно разделить на две группы: с фиксированной системой команд и секционированные. Основное различие этих комплектов заключается в способе реализации устройства управления. В первом случае оно реализовано на комбинационных схемах и конструктивно объединено с арифметическим устройством в одной БИС. Это объединение представляет собой функционально законченный микропроцессор с фиксированной системой команд, ориентированной на широкий круг решаемых задач. Такие МПК обычно имеют стандартные отладочные средства и относительно развитое программное обеспечение, что обеспечивает их широкое применение.

Примером однокристального микропроцессора является центральный процессорный элемент КР580ИК.80. Особенности построения и реализации арифметического и управляющего устройств делают недоступным программисту микропрограммный уровень управления. Он оперирует командами, которые не может изменить. Вместе с тем проектирование конструктивно встраиваемых в РЭА МПУ предполагает их специализацию в соответствии с реализуемым алгоритмом.

Кроме того, как .будет показано в гл. 2, одним из основных требований, предъявляемых к МПУ, является реальный масштаб времени вычислений решаемых алгоритмов. Необходимость специализации системы команд и структуры проектируемых МПУ ограничивает применение однокристальных микропроцессоров в РЭА.

Основной элементной базой конструктивно встраиваемых в РЭА МПУ являются секционированные МПК БИС, у которых в отличие от однокристальных микропроцессоров управляющее устройство реализовано на принципах микропрограммного управления. Такой подход обеспечивает доступ разработчика к уровню микрокоманд, что позволяет изменять команды и соответствующие им микропрограммы исходя из решаемых алгоритмов. Секционированные МПК имеют различные системы команд, разрядность, типы интерфейса ввода-вывода и т. п. Проектируемые на основе секционированных МПК МПУ обладают большой гибкостью, так как расширение функциональных возможностей обеспечивается изменением отдельных микрокоманд или заменой всей памяти микропрограмм.

Построение арифметического устройства требуемой разрядности осуществляется объединением 4-, 8- или 16-разрядных процессорных секций. Микропрограммное устройство управления выполняется на одной или нескольких БИС. Соединив между собой несколько БИС микропрограммного управления, можно увеличить объем микропрограммной памяти. Объединение арифметического и управляющего устройств позволяет получить базовую структуру микропроцессора. Подключение к ней специализированных БИС ввода-вывода, вспомогательных аппаратных микропроцессоров и других специализированных микросхем приводит к повышению производительности МПУ.

Использование секционируемых МПК обеспечивает гибкость проектирования как по аппаратным решениям, так и по реализации требуемой системы команд. Однако при этом предполагается, что разработчик знает возможности и особенности всех микросхем, входящих в состав МПК, принципы объединения их в устройство, организацию синхронизации в устройстве; владеет методами разработки и отладки микропрограмм.

Вместе с тем работа на микропрограммном уровне создает и определенные трудности. Микропрограммный уровень определяется конкретными схемными решениями, поэтому программирование на этом уровне требует от разработчика знаний аппаратных особенностей МПК, учета временных соотношений и т. п. Кроме того, разработка оригинальной .системы команд приведет к необходимости проектирования дополнительных аппаратных средств и программного обеспечения, предназначенного для отладки программ. Это обуславливает увеличение сроков [разработки и повышение стоимости МПУ, проектируемых «а основе секционируемых МПК БИС.

Микропроцессорные комплекты БИС отличаются своими характеристиками, основными из которых являются: число БИС в комплекте, число внутренних магистралей, разрядность, система микрокоманд, число регистров общего назначения, число уровней прерывания, быстродействие, число буферных регистров (портов) ввода-вывода (Явв, ЯВЫв) и др.

Число БИС в комплекте во многом определяет функциональные возможности МПК. Наличие в составе комплекта разнообразных специализированных БИС позволяет проектировать функционально законченные МПУ при минимальном использовании микросхем средней и малой степени интеграции. Если число специализированных БИС в МПК ограничено, то некоторые функциональные узлы приходится проектировать на (микросхемах малой и средней степени интеграция, что снижает плотность упаковки МПУ и ухудшает его конструктивные параметры. Кроме того, использование специализированных БИС для аппаратной реализации некоторых сложных (с вычислительной точки зрения) функций повышает производительность МПУ.

Как было показано в § 1.1, число внутренних магистралей микропроцессорных БИС колеблется от одной до трех. При выборе МПК необходимо учитывать, что уменьшение числа магистралей снижает процент использования площади кристалла под магистрали, а также быстродействие этих микросхем.

Большинство современных МПК имеют разрядность 4, 8 или 16 бит.

Ограничение разрядности обусловлено размерами кристалла и технологическими допусками изготовления логических элементов. Биполярные секционированные МПК обычно имеют разрядность 4 и 8 бит. Разрядность МПК, выполненных по МОП-технологии, достигает 16 бит.

Система микрокоманд (как и число БИС) определяет функциональные возможности МПК. Системы микрокоманд распространенных МПК БИС, их (форматы, разрядность, особенности реализации подробно рассмотрены в [6 — 12]. Отметим, что при выборе типа МПК необходимо, чтобы его система микрокоманд соответствовала решаемому алгоритму. При этом особое значение приобретают микрокоманды, реализующие специальные функции, например умножение, деление, нормализацию чисел и т. п. Эти функции могут быть реализованы аппаратно на специализированных БИС, либо программно, например в МПК БИС КМ1804 [12]. Для ряда применений, не требующих высоких скоростей обработки информации, программная реализация специальных функций может оказаться предпочтительней, так как не требует дополнительных аппаратных затрат.

Число регистров общего назначения (РОН) определяет емкость внутренней сверхоперативной памяти МП и колеблется от 2 до 16. Увеличение числа РОН в МПК дает возможность хранить в них большее число исходных данных и промежуточных результатов вычислений. При этом в микропрограмме вычислений будут шире использоваться микрокоманды типа регистр-регистр, а следовательно, уменьшится число обращений к ЗУ. Быстродействие выполнения такой микропрограммы будет выше.

Прерывание представляет собой процедуру обмена данными с внешними устройствами. При этом инициатором обмена является внешнее устройство, которое посылает сигнал «Запрос на прерывание». Получив этот сигнал, МП приостанавливает выполнение основной программы и переходит к реализации специальной подпрограммы обмена, называемой подпрограммой обработки прерываний. Эта подпрограмма выключает ряд действий, описание которых можно найти в [10, 13].

Число уровней прерывания опре деляет число внешних устройств, способных обращаться к микропроцессору и обмениваться с ним информацией. Этот параметр имеет особое значение при использовании МПК для построения систем сбора и распределения данных, характеризующихся большим числом датчиков информации, имеющих различный приоритет.

Параметром, характеризующим быстродействие МПК, обычно является время цикла выполнения простейшей микрооперации. Поскольку микрокоманды состоят из последовательности микроопераций различной длины, то время цикла выполнения микроопераций дает очень относительное представление о реальном времени реализации микрокоманд. Один из методов определения времени выполнения микрокоманд приведен в Приложении. При совместном включении нескольких арифметических и управляющих устройств с различным быстродействием такт работы всего МПУ определяется длительностью такта устройства, обладающего меньшим быстродействием.

Число буферных регистров (портов) ввода-вывода является параметром, характеризующим структуру МПК БИС. Для секционированных МПК характерно использование многопортовых структур (обычно двух-трех). Увеличение числа портов ввода-вывода приводит к уменьшению длительности цикла выполнения микрокоманды, упрощает построение МПУ, реализованных по «конвейерной» структуре. Остальные параметры МПК такие же, как и у Других цифровых микросхем. Это прежде всего уровни напряжений логических сигналов (U0 и U'), потребляемая мощность, устойчивость к изменениям напряжения питания, коэффициент объединения по входу, коэффициент разветвления по выходу (нагрузочная способность), помехоустойчивость и др.

Функциональная сложность МПК БИС определяется максимальными размерами полупроводниковых кристаллов, изготовление которых может обеспечить современный уровень развития технологии. Небольшие размеры кристаллов (до 50 мм2) требуют упрощения структур и ограничения разрядности БИС.

Для опреде ления содержимого внутренних регистров МП требуются специальные программы, обеспечивающие вывод содержимого регистров из МП. Большее число выводов БИС упрощает разработку МПУ. Однако корпуса, имеющие большее число выводов, занимают большую площадь на плате. Ограниченное число внешних выводов приводит к необходимости использования одних и тех же выводов для нескольких целей, например для ввода и вывода данных.

При построении МПУ необходимо обеспечить электрическое сопряжение между микросхемами МПК БИС. Условиями правильного сопряжения являются одинаковые представления логических О и 1 (U°, U1) и обеспечение допустимой нагрузки на каждый выход. При построении МПУ на одном или электрически совместимых МПК БИС первое условие выполняется и задача электрического сопряжения сводится к обеспечению допустимой нагрузки на каждый выход. Для МПК, выполненных по биполярной технологии, это условна может быть записано в виде неравенства [4]

I1 макс<I1вых, I0макс <I0вых, (1.1)

где I1вых — значение тока, отдаваемого в нагрузку; I'макс — максимально допустимый ток нагрузки, при котором напряжение на выходе соответствует U1; I°ВЫХ — ток микросхемы; I°макс — максимально допустимый ток нагрузки, при котором напряжение на выходе соответствует U0.

Нагрузочная способность по переменному току МПК БИС, выполненных по МДП функционально-технологическому принципу, существенно ниже нагрузочной способности по постоянному току и фактически определяется максимальной емкостью Сн.макс, которую можно подключить к выходу схемы:

CД < Cн.макc, (1.2)

где Сн — емкость нагрузки, складывается из входных Свх и выходных Свых емкостей входов (выходов) микросхем, подключенных к данному выходу, и емкости монтажа См.

Для сопряжения МПК БИС, имеющих различные уровни напряжений логических сигналов, используются специальные схемы, называемые усилителями-трансформаторами уровней напряжений. Например, микросхема К1800ВА4 позволяет сопрягать МПК ЭСЛ и ТТЛ.

Наиболее распространенными являются цифровые микросхемы вообще и МПК БИС в частности, выполняемые по принципам транзисторно-транзисторной логики. Поэтому некоторые микросхемы, выполняемые по другим принципам, могут объединять в кристалле буферные трансформаторы уровней, обеспечивающие по выходу и входу ТТЛ-уровни напряжений логических сигналов.

В настоящее время отечественная промышленность выпускает различные МПК БИС. Технические характеристики и описания этих комплектов приводятся в [6, II4 — 16]. Из известных и освоенных в производстве МПК БИС для использования в РЭА наибольший интерес представляют МПК БИС серий К588, К1800, КР1802, КМ1804. Состав и основные характеристики микросхем, входящих в эти МПК, приведены в табл. 1.2. Подробное описание МПК БИС содержится в [54].

Микропроцессорный комплект БИС КР1802 выполнен по ТТЛШ-функционально-технологичеокому принципу. Электрически программируемая логическая матрица КР556РТ1 позволяет (разработчику записать в «ее оригинальную систему команд, в (Наибольшей степени учитывающую специфику конкретного применения. Наличие матричных умножителей КР1802ВРЗ — КР1802ВР5, а также сумматора на четыре входа обеспечивают значительное повышение производительности МПУ при выполнении арифметических операций. В § 2.1 приведены примеры построения некоторых устройств обработки сигналов на МПК КР1802. Важнейшими особенностями МПК (с точки зрения обработки сигналов) являются [16]:

многопортовая структура БИС. Микросхемы обработки (КР1802ВС1, КР1802ВР1, КР1802ВР2) имеют два порта ввода-вывода; БИС параллельных умножителей КР1802ВРЗ — КР1802ВР5 — три порта, БИС обмена информацией (ОИ) КР1802ВВ1 — четыре, а БИС сумматора — пять портов ввода-вывода. Через эти парты может одновременно осуществляться выборка операндов и выдача результатов обработки. Такая организация БИС ориентирована на эффективное выполнение двухопе-рандовых операций, составляющих большинство (до 80%) всех операций обработки;

использование регистров общего назначения вне обрабатывающих БИС обеспечивает большее быстродействие МПУ, объединяющих несколько разнотипных БИС обработки информации, а также расширяет возможности разработчиков в применении регистров для реализации различных системных функций;

обеспечение конвейерной обработки информации. В БИС обработки информации каждый порт ©вода-вывода имеет регистр, на котором фиксируются операнды или результат. Последовательное объединение этих БИС и управление их входами-выходами позволяет проектировать устройства с конвейерной организацией обработки. Это обеспечивает проектирование МПУ, быстродействие которых определяется временем одного цикла БИС (около 150 нс). Подробное описание МПК БИС КР1802 приведено в [6].

Микропроцессорный комплект БИС КМ1804 выполнен также по ТТЛШ-функционально-техналогическому принципу. Архитектура МПК предусматривает параллельное наращивание разрядности, микропрограммное управление, конвейерную обработку. Эти архитектурные особенности обеспечивают высокую гибкость применения МПК КМ 1804 при построении различных МПУ. В отличие от МПК КР1802 в составе МПК КМ1804 нет БИС, аппаратно реализующих арифметические операции. Вместе с тем МПК КМ1804 отличается большим функциональным разнообразием БИС и, что особенно важно, включает большое число БИС, предназначенных для построения интерфейсных схем ввода-вывода. Комплекты КР1802 и КМ1804 электрически совместимы. Совместное их использование позволит проектировать МПУ обработки сигналов, отличающиеся высокой производительностью и гибкостью. Комплект КМ1804 (является аналогом МПК Ат2900. Построение- различных МПУ на базе Ат2900 подробно рассмотрено в [5, 12].