кратная 4. Система команд по

|

Наименование |

Обозначение |

Тип корпуса |

Основные электрические характеристики |

Примечание |

|

|

16-разрядное наращиваемое АУ |

К588ВС1, К588ВС2 |

Серия K5S8 2124.42 — 1 |

Tц

= 1,0 мкс; 150 логических |

Uп = 5 В±10%. Система |

|

|

Наращиваемая УП |

К588ВУ1 |

2124.42 — 1 |

произведений |

1.1305.909 — 82 |

|

|

Арифметический расширитель |

К588ВР1А — К588ВР1Г |

2124.42 — 1 |

tу<5 мкс; 1=8 бит |

Пвв-выв = 2 |

|

|

Системный контроллер |

К588ВГ1 |

2124.42 — 1 |

Число входов прерываний 7 |

Тц=600 нс |

|

|

Многофункциональный буферный регистр |

К588ИР1 |

2121.28 — 4 |

Tц

= 150 не; l=8 бит |

Пвв=1; Пвыв=1 |

|

|

Магистральный приемопередатчик |

К588ВА1 |

2121.28 — 4 |

Tц=150 нc; l=8 бит |

Пвв-выв=2 |

|

|

Умножитель 16X16 |

К588ВР2 |

4118.24 — 2 |

ty=2 мкс |

Пвв-выв= 1 |

|

|

Кодер-декодер последовательного мультиплексного канала |

К588ВГЗ |

2124.42 — 1 |

Тактовая частота кодера 2 МГц, декодера 12 МГц |

Преобразует код «Манчестер 2» в последовательный униполярный |

|

|

АЛУ |

К1800ВС1 |

Серия К1800 2207.48 — 1 |

U„= — 5,2 В±5%; |

Аналог Мс10800 |

|

|

Микропрограммное устройство управления |

К1800ВУ1 |

2207.48 — 1 |

Uц= — 2 В±5%; Tц = 28 нс; l=4 бит |

Аналог Мс10801 |

|

|

Схема синхронизации |

К1800ВБ2 |

2120.24 — 1 |

Разрядность МК — 8 бит |

Аналог Мс10802 |

|

|

Схема управления ОЗУ |

К1800ВТЗ |

2207.48 — 1 |

1=А бит; Рп=1,6 Вт |

Аналог Мс 10803 |

|

|

Двунаправленный трансформатор уровней |

К1800ВА4 |

2103.16 — 1 |

t3>8 нс; Рп=0,7 Вт |

Аналог Мс1080А |

|

|

8-разрядное АУ |

КР1802ВС1 |

Серия КР1802 2206.42 — 1 |

Гц = 120 не |

Uи=5 В±10% |

|

|

Блок регистров общего назначения (16X4) |

КР1802ИР1 |

239.24 — 2 |

Гц=45 не |

Ри=1,4 Вт |

|

|

Арифметический расширитель |

КР1802ВР1 |

2206.42 — 1 |

Гц-90 не; г-16 бит |

||

|

Схема обмена информацией (4X4) |

КР1802ВВ1 |

2206-42 — 1 |

Гц = 60 не; Рш=1Л Вт |

Пвв-выв = 4 |

|

|

Схема интерфейса |

КР1802ВВ2 |

2206.42 — 1 |

Гц = 100 не |

Рп=1 Вт |

|

|

Электрически программируемая логическая матрица |

К.Р556РТ1, КР556РТ2 |

2121.28 — 1 |

48 логических произведений |

Pп= 0,8 Вт |

|

|

Умножитель последовательный (8X8) |

КР1802ВР2 |

2206.42 — 1 |

tт>1,0 мке; tД>1,8 мкс |

Пвв-выв = 2; Рп=1,5 Вт |

|

|

Умножитель параллельный (8X8) |

КР1802ВРЗ |

2206.42 — 2 |

tу=200 не; Рп = 3 Вт |

||

|

Умножитель параллельный (12X12) |

КР1802ВР4 |

2136.64 — 1 |

tу=200 не; Рп=4 Вт |

Пвв=2; Пвыв=1 |

|

|

Умножитель параллельный (16X16) |

КР1802ВР5 |

2136.64 — 1 |

ty=200 не; Рп=5 Вт |

Пвв=2; ПвыВ=1 |

|

|

Сумматор на четыре входа |

К.Р1802ИМ1 |

2207.48 — 1 |

tс

= 150 не |

Пвв=4; Пвыв=1 |

|

|

4-разрядная процессорная секция |

КМ1804ВС1 |

Серия КМ1804 2123.40 — 6 |

Uв=5 В±10%; Гц

= 110 не. Разрядность — кратная 4. Система команд по ОСТ 11.305.909 — 82 |

Аналог Ат2901 |

|

|

Схема формирования ускоренного переноса |

КМ1804ВР1 |

201.16 — 16 |

Аналог Ат2902 |

||

|

Схема управления последовательностью мк |

КМ1804ВУ1, КМ1804ВУ2 |

2121.28 — 1 2121.28 — 1 |

Аналоги: Ат2909 Ат2911 |

||

|

Схема выбора адреса следующей мк |

КМ1804ВУЗ |

201.16 — 16 |

16 инструкций |

Ат2918 |

|

|

Параллельный 4-разрядный регистр |

КМ1804ИР1 |

201.16 — 16 |

Гц=20 не; Рп=0,65 Вт |

Ат2918 |

|

|

4-разрядная процессорная секция |

КМ1804ВС2 |

2123.40 — 6 |

Число РОН 16 |

Ат2903 |

|

|

Схема управления состоянием и сдвигами |

КМ1804ВР2 |

2123.40 — 6 |

t3

— 60 не. Число шин 2 |

Ат2904 |

|

|

Схема управления микропрограммой |

КМ1804ВУ4 |

2123.40 — 6 |

Гц=95 не; Рп=1,7 Вт |

Ат2910 |

Микропроцессорный комплект БИС К1800 выполнен по ЭСЛ-функционально-технологическому принципу. Микросхемы отличаются повышенными быстродействием и потребляемой мощностью. Архитектура МПК К1800, как и предыдущих, обеспечивает наращивание разрядности, микропрограммное управление, конвейерную организацию вычислений. Отличительной особенностью ЭСЛ-комплекта является ограниченный функциональный состав БИС, что затрудняет построение законченных МПУ только на МПК К1800. Комплект БИС К1800 электрически совместим с цифровыми микросхемами серий К500, К1500. Наличие в составе комплекта двунаправленного транслятора К1800ВА4 позволяет использовать совместно с К1800 МПК БИС ТТЛШ, например КР1802, КМ1804. При построении МПК К1800 использовался ряд схемотехнических и конструктивно-технологических особенностей построения быстродействующих микросхем, что позволило достигнуть степени интеграции до 1000 логических элементов (ЛЭ) на кристалле, снизить потребляемую мощность до 4 — 5 мВт на один ЛЭ и обеспечить время задержки 1 — 1,5 не на один ЛЭ [16].

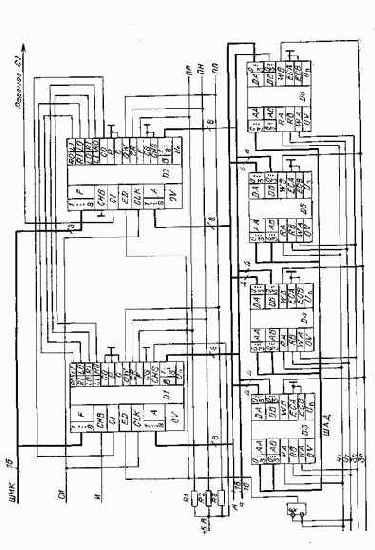

Рис. 1.3. Функциональная схема операционного устройства, построенного на МПК БИС К.Р1802

Микропроцессорный комплект БИС К588 выполнен по КМОП-функцианально-технологичесшму принципу. Важнейшей отличительной особенностью таких микросхем является низкая потребляемая мощность. В статическом режиме потребляемая мощность на один ЛЭ примерно в 100 раз меньше, чем у ТТЛ ЛЭ. В динамическом режиме (мощность, потребляемая КМОП-ехемами, увеличивается при повышении тактовой частоты. При тактовой частоте 1 — 2 МГц она всего в 5 — 10 раз меньше мощности, потребляемой ТТЛ-схемами. Комплект БИС К588 имеет несколько меньшее быстродействие, чем ТТЛШ МПК. Однако МПК К588 обеспечивает построение МПУ РЭА с ограниченным потреблением энергии.

Рассмотрим несколько примеров построения различных аппаратных средств на базе рассмотренных МПК БИС.

Пример 1.1. На рис. 1.3 приведена схема 16-разрядного операционного устройства МП [17].

Операционное устройство выполняет арифметические и логические операции над битами, полями битов, 16-разрядными словами; сдвиг 16-разрядных слов на один разряд вправо и влево. Управление работой операционного устройства осуществляется по шине микрокоманд (ШМК) и шине адреса (ШАД). Передача операндов осуществляется по шинам А и В, результат операции выдается на шину А.

Синхронизация считывания информации из регистров и записи результата в регистр выполняется синхроимпульсом (СИ), импульсами чтения (Чт), импульсами записи (Зп). Результат операции сопровождается выдачей признаков равенства нулю (ПН) результата, переполнения разрядной сетки (ПП) и расширения (ПР). Арифметическое устройство выполнено на двух БИС КР1802ВС1 (Dl, D2). Сверхоперативная память данных и результата выполнена на четырех БИС РОН КР1802ИР1 (D3 — D6). Емкость памяти 16X16.

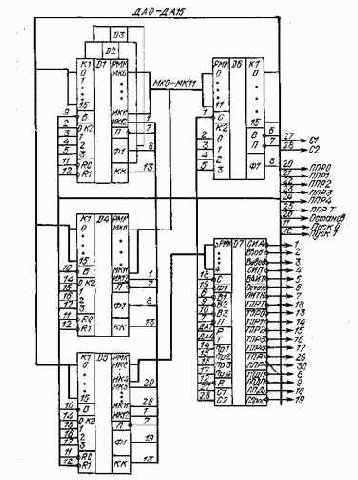

Пример 1.2. Процессор микро-ЭВМ общего назначения. На рис. 1.4 приведена функциональная схема процессора с системой команд и интерфейсом микро-ЭВМ «Электроника-60» [18]. Процессор предназначен для применения в МПУ с жестко ограниченными энергетическими ресурсами и быстродействием до 400 тыс. коротких операций. При этом может быть использовано математическое обеспечение микро-ЭВМ «Электроника-60». Процессор выполнен на БИС МПК К588: К588ВС2 (D6), К588ВУ2 (D1 — D5), К588ВГ1 (D7). Каждая БИС управляющей памяти (D1 — D5) отличается информационным содержанием.

Рис. 1.4. Функциональная схема микропроцессора, построенного на МПК БИС К588

Данные адреса и команды передаются по 16-разрядной совмещенной магистрали данных-адреса ДА0 — ДА15. Эта магистраль соединена с каналом К1 D6 и регистрами команд управляющей памяти (Dl — D5).

Четыре БИС (Dl — D4) формируют микрокоманды, управляющие работой ДУ (D6). 12-разрядные МК объединяются по схеме «проводное И» и подключаются к регистру микрокоманд АУ. Системный контроллер (СК) К588ВП управляется 5-разрядной МК, формируемой D5. Свободные разряды МК (МК5 — МКИ) вырабатывают сигналы разрешения прерывания по запросам ППРО — ППР4, ППРТ и сигнал «Останов».Поскольку длина микропрограмм, записанных в Dl — D5, различная, синхронизация приема кода команды осуществляется по сигналам «Конец команды», объединенным по схеме «Про» водное И».