МИКРОСХЕМЫ, СОДЕРЖАЩИЕ ЭЛЕМЕНТЫ ПАМЯТИ

Микросхема К155ТМ2 (рис. 5.27, табл. 5.18). Эта микросхема содержит два D-трштера. Поясним работу D-триггеров микросхемы К155ТМ2, пользуясь табл. 5.18. Каждый D-триггер этой микросхемы имеет вход предустановки S и сброса R. Из таблицы видно, что при подаче низкого уровня на вход S на прямом выходе триггера Q появится высокий уровень, а на инверсном выходе Q - низкий Уровень. Низкий уровень на входе R устанавливает выходы триггера в противоположные состояния. Если низкий уровень присутствует хотя бы на одном из входов S или R, то сигналы на входах С и D никак не влияют на состояние триггера. Если сигнал низкого уровня подавать одновременно на входы S и R, то на обоих выходах (прямом и инверсном) установится высокий уровень; если эти сигналы одновременно снять, то триггер может установиться в любое состояние, поэтому такой ситуации необходимо избегать.

Рис. 5.27. Микросхема К155ТМ2

| Таблица 5.18 | |||||

| Входы | Выходы | ||||

| S | R | С | D | Q | Q |

| L | Н | X | X | Н | L |

| Н | L | X | X | L | H |

| L | L | X | X | Н | H |

| Н | Н | L | X | Qs | Qs |

| Н | Н | Н | X | Qs | Qs |

| Н | Н | 1 | X | Qs | Qs |

| Н | Н | t | Н | Н | L |

| Н | Н | t | L | L | H |

Рис. 5.28. Временная диаграмма работы микросхемы К155ТМ2

Буквой Qs в табл. 5.18 обозначено состояние триггера, которое было до подачи указанных управляющих сигналов. Из табл. 5.18 видно, что низкий уровень, высокий уровень, а также переход от высокого к низкому уровню на входе С никак не влияют на состояние триггера. Только переход от низкого уровня к высокому устанавливает на выходе триггера тот уровень, который в данный момент присутствует на входе D, а на инверсном выходе устанавливает инверсный уровень. На рис. 5.28 приведена временная диаграмма, иллюстрирующая работу D-триггера микросхемы К155ТМ2.

Таблица 5.19

| Входы | Выходы | ||

| С | D | Q | 0 |

| L | X | qs | Qs |

| Н | Н | Н | L |

| Н | L | L | Н |

Рис. 5.29. Микросхема К155ТМ7

Рис. 5.30. Временная диаграмма работы микросхемы К155ТМ7

Микросхема К155ТМ7 (рис. 5.29, табл. 5.19). Эта микросхема содержит четыре D-триггера.

Каждый триггер имеет вход D, выходы Q и Q и управляющий вход С, но управляющие входы всех триггеров не подключены к отдельным выводам микросхемы, а соединены попарно и подключены к выводам 4 и 13. Поэтому триггерами этой микросхемы нельзя управлять по отдельности. Из табл. 5.19 видно, что если на управляющем входе С низкий уровень, то уровень сигнала на выходе триггера Q остается неизменным, а если высокий уровень, то уровень сигнала на выходе триггера повторяет уровень на входе D. Временная диаграмма, поясняющая работу триггера, приведена на рис. 5.30. Триггер такого типа часто называют "защелкой", так как с его помощью можно в любой момент зафиксировать уровень какого-либо сигнала.

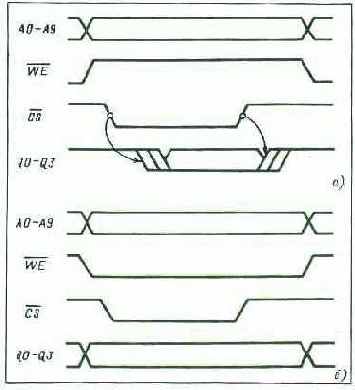

Микросхема КР541РУ2 (рис. 5.31). Эта микросхема является оперативным запоминающим устройством емкостью 4 Кбит с организацией 1024x4 бита. Это значит, что внутри микросхемы содержится 1024 запоминающие ячейки, каждая из которых состоит из четырех двоичных разрядов. Для адресации ячеек памяти внутри микросхемы имеется 10 адресных входов АО — А9. Каждой комбинации сигналов на этих входах соответствует одна ячейка. Для передачи информации в ячейки памяти при записи и из ячеек памяти при считывании имеются выводы QO — Q3. При записи информации эти выводы работают как входы, а при считывании — как выходы с открытым коллектором. Вход WE управляет режимом записи и считывания: при высоком уровне на этом входе микросхема работает в режиме считывания, при низком — в режиме записи. Вход CS управляет работой выводов QO — Q3. При высоком уровне на этом входе информация не может быть считана или записана. В режиме считывания низкий уровень на входе CS разрешает работу выводов QO — Q3 как выходов, а в режиме записи — как входов. Временные диаграммы работы микросхемы в режиме записи считывания приведены на рис. 5.32.

Микросхема КР556РТ4 (рис. 5.33). Эта микросхема явля ется постоянным запоминающим устройством емкостью 1 Кбит с организацией 256x4 бита, т. е. внутри микросхемы содержится 256 ячеек памяти, каждая из которых состоит из четырех разрядов. Информация, записанная в ПЗУ, не стирается при выключении напряжения питания. Для записи информации в ПЗУ используется специальное устройство, называемое программатором. Схема программатора для микросхемы К556РЕ4 (старое название микросхемы КР556РТ4) и режим записи информации не приводятся в этой книге.

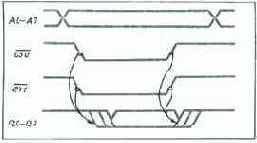

Микросхема КР556РТ4 имеет восемь входов АО-А7 для адресации ячеек памяти, четыре выхода с открытым коллектором QO — Q3 для считывания содержимого ячейки и два управляющих входа CSO и CS1. Считывание информации может происходить только тогда, когда на обоих входах CSO и CS1 низкий уровень (рис. 5.34).

Рис. 5.31. Микросхема КР541РУ2

Рис. 5.33. Микросхема КР556РТ4

Рис. 5.32. Временная диаграмма работы микросхемы КР541РУ2

Рис. 5.34. Временная диаграмма работы микросхемы КР556РТ4 при считывании